�����̂̐������@

���̃y�[�W�ł́A�����܂łʼn�����Ă��܂����u�_�C�I�[�h�v��u�g�����W�X�^�v�Ȃǂ̔����̂��A�ǂ̂悤�ɂ��Đ�������Ă���̂����Љ�܂��B

�����͔̂��ɏ����ȕ��i�ł��B���̈�����������ő@�ׂ������߂��܂��B�ǂ̂悤�ȉߒ����o�č����̂��w�Ԃ��Ƃɂ���āA�������𗝉��ł���悤�ɂȂ�܂��B�܂��A�{�͂ł́A�����̂𖧏W�������A�u�W�ω�H�v�ɂ��Ă����킹�Ă��Љ�܂��B

�����̂̐������@

�_�C�I�[�h��g�����W�X�^�Ȃǂ́u�����̂̐������@�v�ɂ��Đ������܂��B

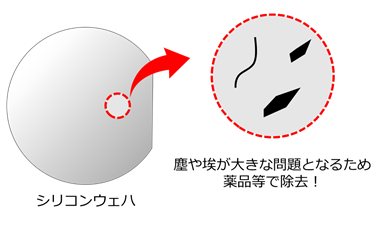

�����̂́A�V���R�����Ɂu�����Ȃǂ̖��v��ςݏd�˂Ă����܂��B���ɏ����ȃX�P�[���̐��E�ƂȂ邽�߁A�V���R����̏��x��A���̏����ȃS�~���傫�Ȗ��ƂȂ��Ă��܂��B

�����̐����̃T�C�N���́A��G�c�Ɏ����Ɖ��}�̂悤�ɂȂ�܂��B

���ɁA�����̍H�����ڍׂɐ������Ă����܂��B

|

�@�V���R���̐�o��

�u�C���S�b�g�v�ƌĂ��A�V���R����̃x�[�X�ƂȂ�傫�ȃV���R���̒P�����_����A�����̂̊�ƂȂ锖����ɃV���R�����o���Ă����܂��B

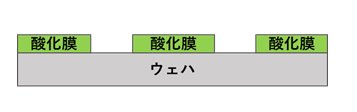

���̐�o�����V���R�����A�u�V���R���E�F�n�v�A�ʏ́u�E�F�n�v�ƌĂт܂��B�E�}�̂悤�ɁA�E�F�n�͉~�̈ꕔ���������`��ƂȂ��Ă���܂��B����͌�H���ŁA����ɐ�o���ۂ̊p�x��ɂ��邽�߂̂��̂ł��B

���݂ɁA�����̂Ɏg�p�����V���R���̏��x�́u�C���u���E�i�C���v�ƌ����A�u�X�X�D�X�X�X�X�X�X�X�X�X���v�Ƃ����l���v������܂��B |

|

|

�A���

���ɁA�N���[�����[���ŁA��o�����E�F�n���܂��B�����̂͐o��ق��肪�t�������܂܂ł��Ƒ傫�Ȗ��ƂȂ邽�߁A��i�Ȃǂɂ���Ă��ꂢ�ɐ��܂��B

�i�N���[�����[���Ƃ́A1�������[�g��������̐o�E���̐������䂳�ꂽ��C����x���m�ۂ��ꂽ�����̂��Ƃł��B�j |

|

|

�B����

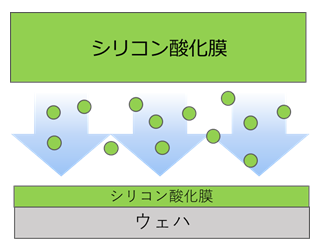

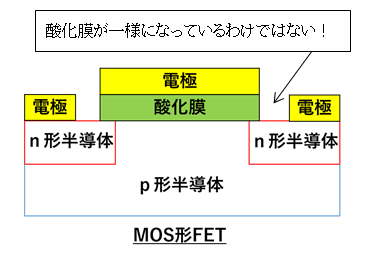

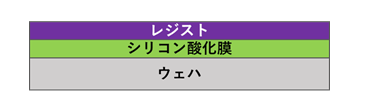

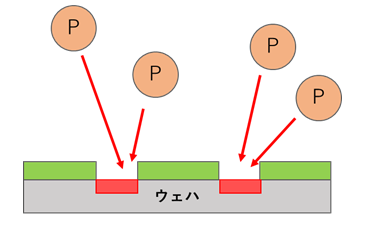

���ɁA���ꂢ�ɐ�ꂽ�E�F�n�̏�ɁA�_�������悹�Ă����܂��B���@�͗l�X�ł��B�i�}�̓E�F�n�̒f�ʂ������j

�Ⴆ�A�_�����̏ꍇ�A�����ɉ��M�����F�̒��Ŏ_�f�␅�f�Ȃǂ̃K�X�����A�_����������@������܂��B�܂��A�V���R���_�������v���Y�}�ɂ���Ċg�U�����A�E�F�n��ɒ��ږ����`��������u�X�p�b�^�v�ƌĂ����@��������܂��B |

|

|

�C���\�O���t�B

���̎_������d�ɂ��Ӑ}�����`�ɂ��Ă����܂��B |

; ; |

|

���̃p�^�[�����쐬����Z�p���A�u���\�O���t�B�v�ł��B�����̐����̊̂ƂȂ�H���ƂȂ�܂��B |

; ; |

| �܂��A�E�F�n��� �u���W�X�g�v �Ƃ���������h�z���܂��B���W�X�g�͎��O�����𗁂т����������Ȗ�i�ɂ���Ɨn���ĂȂ��Ȃ鐫���������Ă��܂��B |  |

|

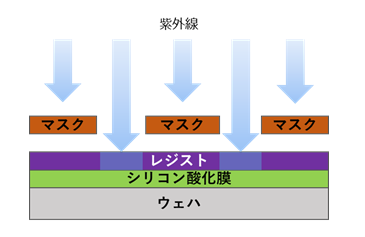

�E�F�n�̏�Ɂu�}�X�N�v�ƌĂ�錊���J���������悹�A���O�����Ǝ˂��܂��B�i�I���j |

|

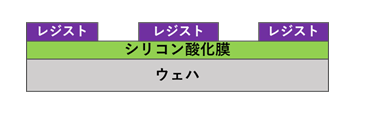

| ���̏�Ԃ̃E�F�n�����Ȗ�i�ɂ��邱�Ƃɂ���āA���O���������������W�X�g�������n���ĂȂ��Ȃ�܂��B�i�����j |  |

|

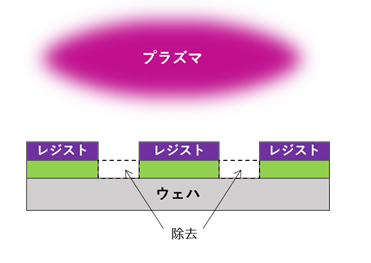

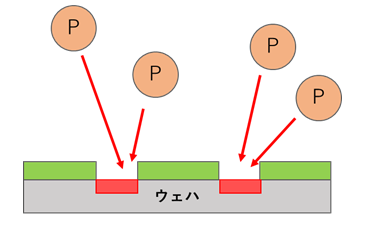

���ɃE�F�n���G�b�`���O�Ƃ����H�����{���܂��B����̓E�F�n��̎_������r������H���ƂȂ�܂��B

�_�����̏����ɂ͂�������@������A�v���Y�}�ɂ�蕨�������������A��i�ɂ����肷����@������܂��B

���̂Ƃ��A���W�X�g���c���Ă��镔���͕ی삳��A�G�b�`���O�ɂ�������܂���B |

|

|

�Ō�Ƀ��W�X�g���i�ɂ���ď�������ƁA�c�������_�����������c��E�F�n�̊����ł��B

���ꂪ���\�O���t�B�ł��B

��肽���f�q�ɂ���āA���\�O���t�B�Ɛ������J��Ԃ�����A���Ԃ��O�サ���肷��ꍇ������܂��B |

|

|

�D�s�����g�U

������z�E�f���̕s�������E�F�n�Ɋg�U���A���`�����̂���т��`�����̂��쐬���܂��B |

|

|

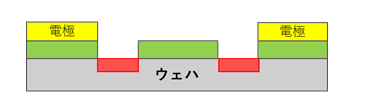

�E�d�ɍ쐬

�_������s���������̂̏�ɓd�ɂ��쐬���܂��B�d�ɂɂ��p�^�[��������̂ŁA���\�O���t�B�Z�p��p���ď��]�̉ӏ��ɓd�ɂ��쐬���܂��B

����őf�q�̊����ƂȂ�܂��B |

|

�W�ω�H�̊T�v

�W�ω�H�͂��̖��̒ʂ�A�E�F�n��ɑ����̑f�q���W�ς������i�ł��B�W�ω�H��ɂ͎�Ɂu�����́v���悹���܂��B�쐬���@�͊�{�I�ɔ����̂Ɠ����ł��B

���W�ω�H�̕���

�W�ω�H���ǂ�قǂ̑f�q���W�ς��Ă���̂��Ƃ����ƁA��20�̂��̂�����APC���̒��ɓ����Ă���悤�ȁA���悻10�̂V��ȏ���̑f�q���l�ߍ��܂�Ă�����̂�����܂��B�W�ω�H�͂��̏W�ϓx���ɂ�艺�L�̂悤�ɕ��ނ���Ă���܂��B

| �f�q�� | ���� |

| ��109�ȏ� | GSI (Giga Scale �W�ω�H) |

| ��107�ȏ� | ULSI (Ultra Scale �W�ω�H) |

| ��105�`107�� | VLSI (Very Large Scale �W�ω�H) |

| ��103�`105�� | LSI (Large Scale �W�ω�H) |

| ��102�`103�� | MSI (Medium Scale �W�ω�H) |

| ��102�ȉ� | SSI (Small Scale �W�ω�H) |

���W�ω�H�̑f�q

�W�ς�����f�q�ɂ��Ăł����A�W�ς���Ɍ����Ă�����̂ƌ����Ă��Ȃ����̂�����܂��B�܂��_�C�I�[�h��g�����W�X�^�Ȃǂ̔����̂͏��^�����\�ŁA�W�ς��邱�Ƃ��ł��܂��B�܂��A��R�������̂Ŏ������邱�Ƃ��ł��A�W�ω�H�ɂ͍̗p����܂��B

���ɁA�R���f���T��R�C���Ƃ��������̂͂ǂ����Ă��傫�����K�v�ƂȂ�W�ω�H�ɂ���ɂ͓���ł��B

�ȏ�Ŕ����̂̐������@�ƏW�ω�H�̂��Љ���I���܂��B

�d�C���킩��Ȃ��@�B�Z�p�҂ł��A�d�q��H�𗝉��ł���I�g�����W�X�^�A�_�C�I�[�h������������Ȃ��Ă����v�I��H���C���[�W���A�I�y�A���v��f�W�^����H�܂ŗ����ł���

�Ǝ��J�����ꂽMONO�m�́u�X�e�b�v���w�K�v���O�����v���@�l�̗p���сF�V�O�O�Јȏ���

�J�e�S���[���j���[

�@�B�v�̊�b���w��

�@�B�v�̊�b���w��

�RDCA�̊�b���w��

�RDCA�̊�b���w��

�ޗ��͊w�̊�b���w��

�ޗ��͊w�̊�b���w��

���̗͊w�̊�b���w��

���̗͊w�̊�b���w��

���^�̊�b���w��

���^�̊�b���w��

�@�B���H�̊�b���w��

�@�B���H�̊�b���w��

�@�B�v�f�̊�b���w��

�@�B�v�f�̊�b���w��

�RD�v�����^�[�̊�b���w��

�RD�v�����^�[�̊�b���w��

�����ޗ��̊�b���w��

�����ޗ��̊�b���w��

���}�̊�b���w��

���}�̊�b���w��

�RDCAD�̉��p���w��

�RDCAD�̉��p���w��

�M�͊w�̊�b���w��

�M�͊w�̊�b���w��

�@�B�͊w�̊�b���w��

�@�B�͊w�̊�b���w��

���^�̎��H���w��

���^�̎��H���w��

���^����T�̃|�C���g

���^����T�̃|�C���g

CAE��͂̊�b���w��

CAE��͂̊�b���w��

�v���X�`�b�N�̊�b���w��

�v���X�`�b�N�̊�b���w��

�d�C�̊�b���w��

�d�C�̊�b���w��

�X�|���T�[�h �����N